Project Title: - Area-Efficient

Arithmetic Expression Evaluation Using Deeply Pipelined Floating-Point Cores

Abstract :- :-

Recently, it has become possible to implement

floating-point cores on field-programmable gate arrays (FPGAs) to provide

acceleration for the myriad applications that require high-performance

floating-point arithmetic. To achieve high clock rates, floating-point cores

for FPGAs must be deeply pipelined. This deep pipelining makes it difficult to

reuse the same floating-point core for a series of dependent computations. However,

floating-point cores use a great deal of area, so it is important to use as few

of them in an architecture as possible. In this paper, we describe

area-efficient architectures and algorithms for arithmetic expression

evaluation. Such expression evaluation is necessary in applications from a wide

variety of fields, including scientific computing and cognition. While

best-suited for particular classes of expressions, the proposed designs can

evaluate general expressions as well. Additionally, multiple expressions can be

evaluated without reconfiguration. Experimental results show that the areas of

our designs increase linearly with the number of types of operations in the

expression and that our designs occupy less area and achieve higher throughput

than designs generated by a commercial hardware complier.

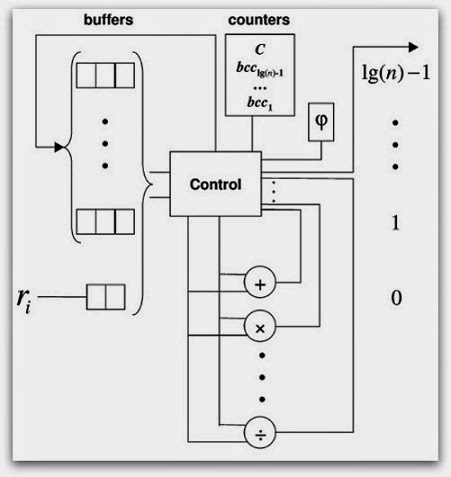

Block

Diagram

Existing

Sytem

Developing

high-performance floating-point designs on FPGAs is still challenging. Because

of their complexity, the floating-point cores have very large areas.

Proposed

System

In

this paper, we propose a high-performance and area-efficient solution to the

arithmetic expression evaluation problem.

Applications

·

Arithmetic processor

·

DSP

Software Used

·

Modelsim : Simulation Software

0 comments :

Post a Comment